Received: Sep '22

Revised: Accepted: Oct '22

© 2022 by the authors. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

## AN EFFECTIVE DATA ENCRYPTION USING AES CIPHER WITH SRAM BASED SOFT-ERRORS ON FPGA

# Aravindhan Algarsamy<sup>1</sup> and Shaik.Hafijulla Irshad<sup>2\*</sup>

E-mail: <sup>2\*</sup>hafeezshaik814@gmail.com

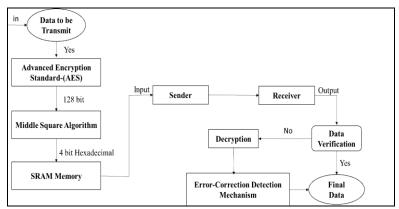

Among validation procedures on the web, the fascinating information encryption context is the foremost usual strategy, and it is employed more effortlessly and successfully than other methods. However, it may be helpless against attacks such as listening quietly and snooping. This issue was overcome by using this Strategy for information security. The most widely used Strategy is one that is based on the enhancement of errors. The later inquiry exhibits the shortcoming of the slight changes. As a result, we developed a module that utilizes a different method. In today's world, secret writing provides an important function in information security. It is muddled data that cannot be accessed without the use of a key. It is controlled by AES (128 bits) followed by Middle Square Algorithm. As in SRAM information as an input to yield, besides information confirmation module was made, and then final information was decoded.

Keywords: Ciphertext, Middle Square Method, SRAM, Error Correction/Detection Mechanism.

## 1. INTRODUCTION

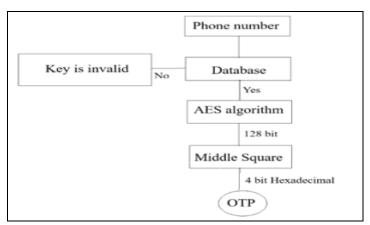

It is a protected method for gaining admittance to a particular exchange or information data. To do as such, we utilized the AES figure text created by AES and changed it over to a digit or byte number. As the calculation is scrambled, it is more challenging to unravel. As information, we will give a telephone number and the data set will check whether the number is related to a specific record. In this paper, we will initially make an information base of telephone numbers for a specific record [1], [2]. On the off chance that it isn't in the data set, then, at that point, the following module won't be executed, i.e., the cycle will be ended. On the off chance that the number matches, we will continue to the following module - AES. AES is an uneven calculation that utilizes the telephone number as a key. Then, at that point, figure message is shipped off the following module which utilizes the center square technique. This is a basic hashing strategy that squares input and chooses center numbers. These numbers fill in as hexadecimal information [3]. These delicate mistakes conjointly alluded to as worldly blunders, are the point at which the info information can be gathered from SRAM memory and shipped off the shipper as info information and the module then sends similar information back to the source [4]. The encrypted information then goes through information confirmation. On the off chance that information is checked to be input information, the information continues to be definite information. Thus, the present credulous

clients have progressively been designated by scoundrels who are trying to acquire a simple benefit through unlawful exchanges. There are many kinds of assaults, including snooping, phishing, parodying, a man in the center, Denial-of-administration, and infection assaults [5]. Confirmation techniques, for example, marks, personality cards, pins, and so on don't give adequate protection from these assaults.

## 2. SYSTEM BLOCK DIAGRAM

As a generally utilized instrument, the product bundle utilized in this paper is Xilinx VIVADO, and the language is Verilog. In the first place, we should assemble modules inside the model for every individual, and afterward, we need to make a visual point of interaction utilizing Verilog code. During the primary period of this article, we ought to incorporate information that incorporates a rundown of telephone numbers related to a specific record. With the ceaseless scaling of construction size, framework crashes because of programming mistakes are turning out to be increasingly more typical in CMOS innovation. Programming bugs seriously affect reconfigurable gadgets considering static irregular access memory (SRAM), since a blunder in the setup pieces can for all time change the usefulness of the framework. Since interconnect assets are the primary supporter of arrangement memory disappointments in based plans, framework disappointment rate can be fundamentally diminished by relieving delicate

blunders in the directing texture. In the first place, this paper presents a complete examination of the vulnerability of SRD change boxes to short and open deficiencies. Considering this investigation, we present a solid directing construction by proficiently utilizing kelter SRAM cells in the setup memory [6]. The proposed conspire is exceptionally adaptable and equipped accomplishing any ideal degree of unwavering quality. In the proposed conspire we additionally present a mistake covering component alleviating the effect of delicate blunders. For instance, info can make a motion, and information will decide if the sign is in the

information or not. On the off chance that it isn't in the information base, the accompanying module won't work, or at least, the way will be halted. Assuming the telephone number is entered in a similar sign mode, the cycle continues to the following module the AES module. AES might be an intelligible science recipe called Integrate Nursing involving a sign as an info key [6]. Then the code text is dispersed to the following medium-sized module. this is normally a straightforward hashing strategy that can square information and select middle numbers. Here we typically take the digits in the square inside Fig.1 showing the series of steps to follow.

**Proposed Method**

Before, the utilization of RSA through method of method for Login System transformed into focused on holding the non-public key at the server. Nonetheless, this procedure is restricted, wherein the entire gadget might be abused each time a secret mystery is found. Subsequently, this paper shows an unprecedented strategy in which the RSA secret key used to substitute the OTP secret is put away at the buyer side, while the overall population key and modulus are saved at the site. Moreover, as a protection degree from assailants, an OTP secret is produced at the server [4]. When made at the buyer side, aggressors can set off each the encoded key and the scrambled secret phrase. Preferably, they could transport them each to the server without coding and without getting the secret key. What's more, the RSA framework at the server is an arrangement of encryption best. That approach takes up the PC charges of secluded exponentiation because of the reality the overall population secret is continually more modest in contrast with the nonpublic key. Assuming we depend on that a buyer's secret key has been found, best the buyer's gadget that might be gotten to can be disregarded, which in all actuality does now never again practice to

various clients [5]. Test impacts show that despite the fact that clients should remember their secret keys and invest additional energy, the proposed new gadget is significantly stronger and more extra secure [8]. Hence, clients who utilize this product can get admission to the application without irritating aggressors.

## 3. SRAM BASED SOFT-ERRORS ON FPGA

There are a couple of added substances inside the AES definition which can like added substances introduced in spic and span FPGAs to convey blunders identification. In this manner, the equality topic isn't utilized for all improvements in AES. for instance, in contrast with going before assessment, a double ported block memory is recruited in Sub Bytes of AES to convey mistakes identification. for sure, duplication is employed for blunder discovery in the making arrangements of the control computerized gadget. By using just some LUTs the upward of the control advanced gadget is low. an oversight in accessory FPGA will quite control the reasonableness of a design. Hence, in the event that those errors don't have all the earmarks of being disposed of through method of method for

reconfiguration, the unwavering quality of an adjustment strategy is problematic. To exact missteps, self-reconfiguration is incontestable sooner or later of this assessment. just if there should arise an occurrence of a mistake commonness, the AES module intrudes on the included processor at the **FPGA** for reconfiguration [3]. The commitments of this assessment incorporate issues as follows. Blunders coming about because of radiation in SRAMprincipally based absolutely FPGA are molded through method of method for double-dealing the pin shortcoming model. Then this honest and precise adequate demonstrating is approved through method of method for reenacting botches inside the design report. Radiation issues are reproduced through method of method for flipping pieces of side interest inside the design report that is downloaded at the FPGA. the ideal web is killed inside the situated and directed netlist to get the changed setup report. Then, at that point, the adjusted and genuine arrangement documents. The shortcomings of the equality concern depend in blunders location are set through a minuscule low style upheld on FPGA [8]. the results of an issue proliferating to yield, while mimicking mistakes through way of approach to flipping pieces in the arrangement report, are found. The mistakes

protection of the equality subject is duplicated from the data course back-peddles to the control computerized gear, trustworthiness hinders, and steering. This improvement is finished through method of method for moderating the shortcomings inside the equality subject on the register-switch The deficiency of renowned blunder adjustment procedures very much like the triple general overt repetitiveness and betting code in is self-reconfiguration **FPGAs** is typically suggested all things considered. AES with the advanced equality subject is assumed related implemented at the FPGA as an informatics center.

Module 1: It is a data set of data and contains telecall cell phone numbers. Since we for the most part will generally utilize the Xilinx Vivado 2019.1 instrument to take advantage of neighboring substances, the data is taken as a pill, including call cell phone numbers. These telecall cell phone numbers are the motivation for the module. You should organize the data to go on with the ensuing module. If the flagging isn't in the structure, then there is no key for the ensuing module I., AES calculation rule. So, the significant things are viewed as zeros that would turn out to be left in the module mistake.

**Existed Method**

Encoding and unraveling are vital squares in correspondence. There are numerous strategies for carrying out mistake discovery and revision code (EDAC). These codes can deal with numerous blunders and depend on limited fields. Number juggling, otherwise called Galois Field. BCH codes can address a predetermined number of pieces at each position, while RS codes bunch bits into blocks for later remedy. RS is an exceptionally famous mistake revision code and has been applied

different circumstances. particularly in Accordingly, correspondence frameworks. an effective blunder control code is expected to safeguard advanced information. correspondence frameworks, Reed-Solomon codes are broadly used to give blunder assurance. because of impedance and organization issues, bringing about blunders. Mistake Correcting Codes (ECC) are an arrangement of numbers created by explicit calculations to recognize and eliminate blunders in

information sent over boisterous channels. Mistake remedy codes decide the specific number of adulterated bits as well as the place of the tainted pieces inside the calculation's requirements. ECCs can be comprehensively grouped into two sorts, block codes and convolutional codes. The Reed Solomon code is a sort of square code.

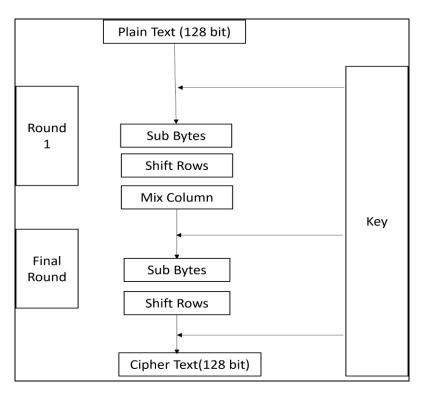

**Module 2**: Contains a 128-digit AES encryption part. The way to AES is this variety at the highest point of the module. Typically, the assortment is 40-piece. In any case, 128 pieces are significant for AES. By and large, AES plays ten adjusts and plays 4 sub-activities like Add Round Key, Sub bytes, Swap Rows and Shuffle Columns.

In the highest point of Fig.2, the 128-digit plaintext is predefined and figure key's the information sign. since the code key size is 128-bit, assortment of rounds (r) performed region unit ten. The code

key's given to Key broadening block that gives keys to each circular. each circular has four sub tasks that should be performed.

| Table 1 Relation between number of rounds(r) and<br>Cipher key size |    |                 |  |  |  |  |  |  |

|---------------------------------------------------------------------|----|-----------------|--|--|--|--|--|--|

|                                                                     | r  | Cipher key size |  |  |  |  |  |  |

|                                                                     | 10 | 128             |  |  |  |  |  |  |

|                                                                     | 12 | 192             |  |  |  |  |  |  |

|                                                                     | 14 | 256             |  |  |  |  |  |  |

|                                                                     |    |                 |  |  |  |  |  |  |

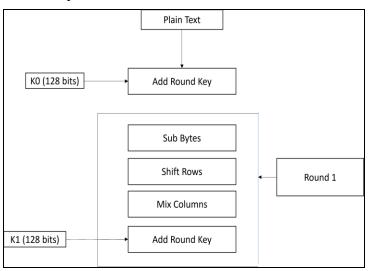

the 128-cycle plaintext is predefined, and the figure key is the information phone number. As the code key size is 128-cycle, number of rounds (r) performed are 10. The code key is given to Key improvement block which gives keys to each change. Each round has 4 sub undertakings that should be performed [7].

It should be clear that this is certainly not a general end (the temporary approach to acting is significantly dependent on the application correspondence plan, the volume of imparted data, and the snapshot of recognizable proof), but it shows how the model can be used for a transient appraisal if the intricate limits can be assessed or surveyed, as well as the capacity of the proposed methodology in supporting clients of coherent applications to arrive at reliable executions. Higher slip-up rates, greater disclosure ranges and calm faults are typical later. It is projected that, in exactable systems, errors will happen a couple of times every day, and they will multiply to create bungles that will go from process slams into defiled

results because of undetected missteps.

## 4. IMPLEMENTATION

The outline of a norm round of AES encryption confined in fig.3. There are four sub-processes in each round. The first-round process is shown fig.3.

Fig.3 Sub operations of AES

In the above Fig.3, It's shown that every single one of the exercises is acted in each round other than in last.

The Bullets excepting the part uniting movement. Replacement of the storing unit (sub bytes): The sixteen data bytes are displaced by a sentence table (s box) in the setup. The thing can be a four-line organization and a four-portion system. four segments are a prisoner on the left. Each entry in the right element of the deleted segment is

reinserted. The change is made as follows: 1) There is no change inside the essential line. 2) The resulting line is moved one (byte) aside. 3) 2 spots are prisoners in the third line on the left. 4) 3 spots are prisoners in the fourth line on the left. The effect would be one more cross-section of sixteen vague yet prisoner bits. Unite Columns: Using an interesting mathematical relationship, each 4-byte fragment is as of now being redone. This technique takes every one of the four bytes of a line as data

and makes four by and large new bytes to override the chief section. A result is a replacement group of sixteen new bytes. Note that this movement isn't performed on the last round. Add roundabout key: The sixteen bytes of the show are correct now seen as 128 pieces and are XORed with the 128 bits of the round key. Expecting this is the last round, the ciphertext is the outcome. These four exercises are performed on each I. round, on numerous occasions. The last outcome is considered the related ciphertext and fills in as commitment to the accompanying module. Substitution of bytes (sub bytes): The 16 data bytes are superseded by a fair table (S-box) in the setup. The thing is a four-line organization and a four-portion structure [8]. Shift pushes: Each of the four lines in the show is moved aside. All eradicated entries on the right 50% of the line are reinserted. The moving is continued as follows: 1) There is no moving in the fundamental line. 2) The resulting line is moved one (byte) aside. 3) In the third line, two spots are moved aside. 4) Move left three spaces in the fourth section. The effect is one more assortment of comparative 16 pieces anyway moved similar with each other. Blend Columns: A remarkable mathematical limit is by and by used to change each four-byte segment. This procedure takes all the four bytes of a line as data and makes four out and out new bytes to displace the principal fragment. The result is one more display with 16 new bytes. Note that this movement isn't performed on the last round. [9] Add round key: the 16 bytes of the bunch are at present considered 128 pieces and the 128 bits of the round key are XORed. Accepting that this is the last round, the ciphertext is yielded. These four errands are acted in each round I. played out different times. The last outcome is considered ciphertext and fills in as commitment for the accompanying module. This file approved the appropriate Verilog code for the proposed model and joined the AES condition and Middle-Sq approach. in the Xilinx Vivado programming pack. In this article, we will make a module that uses another cryptographic computation. Cryptography expects a huge part in data security right now. Cryptography infers making secret codes (ciphertext) that are in an unfathomable design and can't be examined aside from assuming an ideal key is used to disentangle them. The proposed system is the AES computation followed by the mean square method to convey a hexadecimal worth. We will reduce the AES result

to 46 pieces through the mean square method.

It is a safeguarded strategy for getting to a specific trade or data information. To do this, we take AESmade AES ciphertext and convert it to different pieces or bytes. Since the estimation is mixed, it is more difficult to break. As data, we give a phone number, and the informational index will check to assume that the number relates to a specific record. In this record, we at first make an informational collection of phone numbers for a specific record [1], [2] If it is missing in the database, the going with module won't run, or possibly, the cycle will end. Accepting the number matches, we proceed to the accompanying AES module. AES is a lopsided computation that uses the phone number as a key. The ciphertext is then transported off the accompanying module, which uses the mean square procedure. This is a clear hash methodology that squares the data and picks numbers in the center. These numbers fill in as hexadecimal data [3]. the transporter as data and the module then, at that point, sends comparative data to the source. The mixed data then, at that point, goes through data affirmation. Accepting the data is affirmed as data, the data is passed to the last data. Thusly, the present unsuspecting clients are continuously being centered around by crooks expecting to make a straightforward increase from unlawful trades. There are many kinds of attacks including sneaking around, phishing, man-in-the-middle, repudiation of organization, and contamination attacks. Check procedures, for instance, marks, ID cards, pins, etc. don't offer satisfactory confirmation against these attacks. Among endorsement methodology on the Web, the vitally ordinary framework is the captivating setting of information encryption, used with not such a lot of effort but instead more achievement than various strategies. In any case, it might be defenseless against attacks, for instance, calm sneaking around and sniffing. This issue was overpowered with this information security approach. The most used approach relies upon bungle change. Further assessment reveals the shortfall of minor changes. Therefore, encouraged a module that uses a substitute procedure. Right now, secret forming fulfills a huge limit in information security. an enter key. The ciphertext is then scattered to the accompanying medium-sized module.

The essential goal of the proposed controlling design is to use a mix of nothing, and one smoothed out astray SRAM cells in the guiding development

to additionally foster system resolute quality. Zerosmoothed out SRAM cells, which offer tremendous protection from atom impacts that impact zero-to a tiny smidgen shift, are the most suitable for networks in stopped-up districts where short faults are plausible. Get it Moving Network frailty to short-circuits is basically a direct result of the guiding of no less than two associations on a typical channel or shared SM where an unused switch can be accidentally related. The associations are used commonly in the SM or in the directing channel. Likewise. obstructed locales achieve restricted tricky cells than non-hindered areas, since

#### 5. EXPERIMENTAL RESULTS

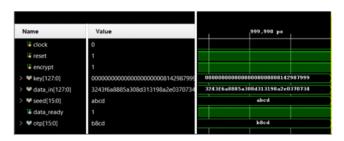

## Case 1: Generation of OTP:

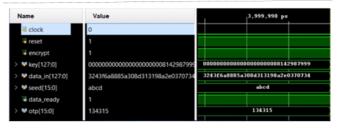

Case 2: Generation of OTP for same Number in Second Attempt:

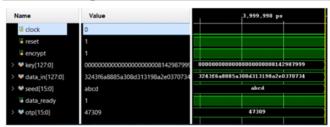

Case 3:Generation of OTP for Same Number in Third Attempt:

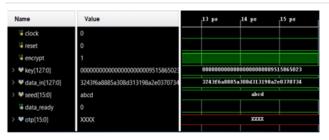

Case 4: Now applied number which is not in Database so OTP not Generated

such a circumstance can happen more from time to time in impeded districts. On the other hand, smoothed-out SRAM cells are sensible for long associations that are more disposed to open blemishes. The familiarity with an association to open weaknesses is essentially affected by the length of the association and the number of branches in the association. Ordinary channel or solely guided on two unmistakable channels, the amount of open sensitive cells would be something basically the same. That is, stop-up doesn't be ensured to impact the number of open-delicate cells.

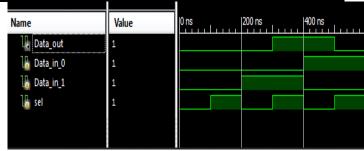

## Mode1:

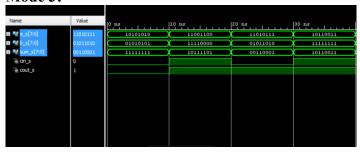

#### Mode 2:

| Name                                | Value   | 18,999,995 ps | 18,999,996 ps | 18,999,997 ps | 18,999,998 ps | 18,999,999 ps | 19,000,000 ps   1 |

|-------------------------------------|---------|---------------|---------------|---------------|---------------|---------------|-------------------|

| ใ∰ clk                              | 0       |               |               |               |               |               |                   |

| la reset                            | 1       |               |               |               |               |               |                   |

| la datain                           | 1       |               |               |               |               |               |                   |

| la dvin                             | 0       |               |               |               |               |               |                   |

| le and2                             | 1       |               |               |               |               |               |                   |

| and1                                | 1       |               |               |               |               |               |                   |

| la ando                             | 0       |               |               |               |               |               |                   |

| Te xor2                             | 1       | No.           |               |               |               |               |                   |

| Un xor1                             | 1       |               |               |               |               |               |                   |

| Ta xoro                             | 1       |               |               |               |               |               |                   |

| Um err                              | 1       |               |               |               |               |               |                   |

| dvout                               | 1       |               |               |               |               |               |                   |

| le code                             | 0       |               |               |               |               |               |                   |

| ▶ datareg[6:0]                      | 1111111 |               |               | 1111111       |               |               |                   |

| <ul> <li>outdatareg[6:0]</li> </ul> | 1010111 |               |               | 1010111       |               |               |                   |

| ► S cntr[2:0]                       | 010     |               |               | 010           |               |               |                   |

## Mode 3:

#### Waveform:

#### FPGA HARDWARE BASYS 2 BOARD:

Waveform:

## 6. CONCLUSION

Since the data is transmitted via AES and stored in SRAM memory. Software errors must be radiation-free and serious knowledge must be transferred to setups for scripting. The encryption becomes more effective, and the error rate decreases. Also, minor errors may occur, in this case we want to use output knowledge error detection and correction mechanism. If inappropriate information is pushed back, only the acquired verification block should

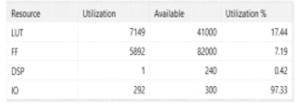

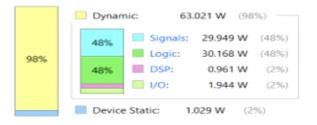

**Table 2. Containing Availability and Utilization of Resources**

**Fig.6 Analysis of Power Supply** provide information during the expansion.

## **Future Scope**

As future work, non-deterministic imitating might be performed to grow the scope of uses that can be secured. Trial approval should to be reached out to applications with client level client characterized designated spots. An ideal designated spot span ought to be determined to limit the normal execution time. then again, the encryption levels are Higher.

## **REFERENCES**

- Narendra Babu T, Noorbasha F, Krishna S, Sai Charan K, Sai Kalyan R, FPGA Implementation of Cryptographic System Using BODMAS Sequence of Operations, 2016, ARPN Journal of Engineering and Applied Sciences, Vol: 11, Issue: 19, p.: 11475 11479, ISSN 18196608

- 2. Narendra Babu T., Noorbasha F., Gunnam L., Implementation of a High Security Cryptographic System with Improved Error Correction and Detection Rate Using FPGA, 2016, International Journal of Electrical and Computer Engineering, vol: 6, Issue: 2, p.: 602 610, ISSN 20888708

- 3. Neelima U., Noorbasha F., Data Encryption and Decryption Using Reedmuller Techniques, 2016, International Journal of Engineering and Technology, Band: 8, Nummer: 1, S.: 83 91, ISSN 23198613

- 4. Jaya Kumar E., Noorbasha F., Design of Static Flip-Flops for Low-Power Digital Sequential Circuits, 2016, International Journal of Engineering and Technology, Band: 7, Ausgabe: 6, Seiten: 2223 2230, ISSN 23198613

- 5. Noorbasha F., Manasa M., Gouthami R., Sruthi s., Priya D., Prashanth N., Rahman M., FPGA Implementation of Cryptographic Systems for

Symmetric Encryption, 2017 Journal of Theoretical and Applied Information Technology, Vol: 95, Issue: 9, pp: 20382045, ISSN: 19928645

- 6. Noorbasha F., Hari Kishore K., Naveen T., Sai Anusha A., Manisha Y., Revathi K., Manasa M."Implementation of Modified Feistel Block Cipher for OTP Generation with Verilog HDL", 2018, Progress In Electromagnetic Research M, Vol. 63, Issue: ,pp. 163 to.: 173, DOI: ,ISSN: 19378726

- 7. Praveen Blessington T., Bhaskara B., Noor Basha F., "Efficient Analysis for Energy

Modeling in Three-Dimensional Network Routing Topologies on Chip Architectures", 2018, Progress In Electromagnetics Research C, Vol. 85, Issue: , S.: 191 an: : 208 ,DOI: 10.2528/PIERC18041906 ,ISSN: 19378718 [8]PraveenBlessington T., Bhaskara B., Basha F., Three-Dimensional Network-on-Chip Architecture", 2018, Journal of Advanced Research in Dynamical and Control Systems, Vol. 10, Issue: 9 Special Issue, S.: 323 bis: 332, DOI: ,ISSN: 194302.